УДК 004

# Построение основных устройств АЛУ ЭВМ с использованием СКМ

Болтовский Гавриил Александрович Приамурский государственный университет им. Шолом-Алейхема Студент

### Аннотация

Целью данной статьи является построение основных устройств арифметикологического устройства электронно-вычислительных машин. Будут рассмотрены схемы для полусумматора, сумматора, RS-триггера и построены с использованием системы компьютерной математики MATLAB & Simulink. Результатом исследования станут построенные логические схемы с подробным описанием их принципов работы.

**Ключевые слова:** АЛУ, MATLAB, схемотехника

# Construction of the main devices of ALU computers using SCM

Boltovsky Gavriil Alexandrovich Sholom-Aleichem Priamursky State University Student

#### **Abstract**

The purpose of this article is to build the main devices of the arithmetic-logical unit of electronic computers. Circuits for the half-adder, adder, RS flip-flop will be built and built using the MATLAB & Simulink computer mathematics system. The result of the study will be constructed logic circuits with a detailed description of the principles of work.

Keywords: ALU, MATLAB, circuitry

### 1. Введение

## 1.1 Актуальность исследования

Исследование арифметико-логического устройства компьютера важно для проектирования и программирования компьютерных систем. Это позволяет исследователям понять принципы работы арифметико-логических устройств и их применение в проектировании и программировании компьютеров. АЛУ используются для выполнения арифметических и логических операций над данными, что позволяет создавать сложные алгоритмы. Также эти устройства применяются для реализации различных процессорных архитектур и для выполнения других вычислений.

## 1.2 Обзор исследований

Принципы построения логических схем в СКМ MATLAB & Simulink изложены в статье [1]. Положения из математической логики и схемотехники

отражены в учебных пособиях В. М. Зюзькова, А. Н. Колмогорова, А. Г. Драгалина [2][3]. Д., Харрис, С. Харрис в своём исследовании так же рассматривают устройства АЛУ [4]. Построение собственных вычислительных устройств интересует многих исследователей [5][6][7].

### 1.3 Цель исследования

Целью исследования является построение основных устройств арифметико-логического устройства электронно-вычислительных машин

### 1.4 Постановка задачи

Будут рассмотрены схемы для полусумматора, сумматора, RS-триггера и построены с использованием системы компьютерной математики MATLAB & Simulink.

### 2. Методы исследования

Важнейшим применением теории булевых функций является создание автоматической техники. Элементы математической логики позволили развиться таким областям техники как конструирование вычислительных машин, электронных и сетевых устройств.

С развитием техники, были созданы устройства, которые работали только с фиксированными сигналами электрического тока. Такие устройства стали называть логическими элементами.

Логический элементом является электронное устройство, которые преобразуют некоторые двоичные входные сигналы по определённому закону. Логические элементы для унарных и бинарных булевых функций являются основными, на базе них создаются другие вычислительные устройства. Логические элементы встречаются и под названием: «логические вентили». У каждого логического элемента есть входы слева и выходы справа; входы есть аргументы функций, который реализует вентиль, а выходы — значения. Инверсия сигнала обозначится кружком на логическом элементе. Ознакомиться с логическими вентилями и их обозначениями в различных стандартах можно в таблице.

Наработки в сфере создания логических схем позволили строить электронно-вычислительные машины, компьютеры

За обработку информации на компьютере ответственно так называемое арифметико-логическое устройство (АЛУ). Оно состоит из ряда устройств, важнейшие из которых — полусумматоры, триггеры, сумматоры, шифраторы, дешифраторы, регистры. Рассмотрим логические схемы некоторых их них.

Двоичный полусумматор (half adder, двухразрядный сумматор, бинарный сумматор, двухбитный сумматор) является устройством, имеющий два входа (A, B) и два выхода (P, S). Таблица истинности полусумматора представлена ниже (табл. 1).

| T ~ 1      | т ~       |            |           |                         |

|------------|-----------|------------|-----------|-------------------------|

| таолина т  | — таолина | истинности | лвоичного | полусумматора           |

| т иолици т | таолица   | nemmeem    | двен шеге | 11031 y C y Minia i Opa |

| А (вход) | В (вход) | Р (выход) | S (выход) |

|----------|----------|-----------|-----------|

| 0        | 0        | 0         | 0         |

| 0        | 1        | 0         | 1         |

| 1        | 0        | 0         | 1         |

| 1        | 1        | 1         | 0         |

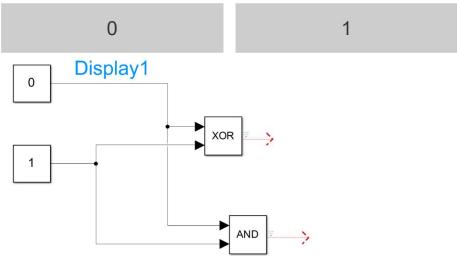

Схема полусумматора представлена на рисунке (рис. 1).

Рисунок 1 – Логическая схема двоичного полусумматора в MATLAB & Simulink

Сложение бинарных чисел можно происходит следующим образом: 0+0=0, 0+1=1, 1+0=1, 1+1=10. То есть каждое из этих чисел можно задать двумя значениями: S – значение суммы, P – значение переноса. Так же видно, что S – исключающее ИЛИ, P – логическое И.

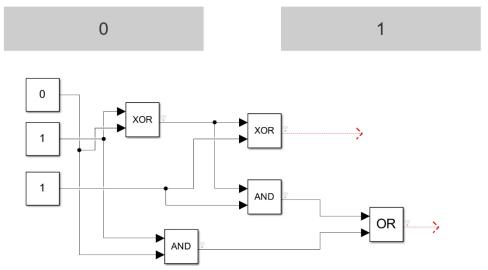

В полусумматоре все вычисление происходят только в самом младшем разряде. Устройство, в котором происходит сложение с учётом значения, переносимого из предыдущего разряда, называется одноразрядным двоичным сумматором (adder, полный сумматор, полный однобитный сумматор). Имеет три входа и два выхода (табл. 2).

Таблица 2 – Таблица истинности двоичного сумматора

| А (вход) | В (вход) | P | S | $\mathbf{P_0}$ |

|----------|----------|---|---|----------------|

| 0        | 0        | 0 | 0 | 0              |

| 0        | 1        | 0 | 1 | 0              |

| 1        | 0        | 0 | 1 | 0              |

| 1        | 1        | 0 | 0 | 1              |

| 0        | 0        | 1 | 0 | 0              |

| 0        | 1        | 1 | 1 | 0              |

| 1        | 0        | 1 | 1 | 0              |

| 1        | 1        | 1 | 1 | 1              |

Схема полусумматора представлена ниже (рис. 2).

Рисунок 2 –Логическая схема полного сумматора в MATLAB & Simulink

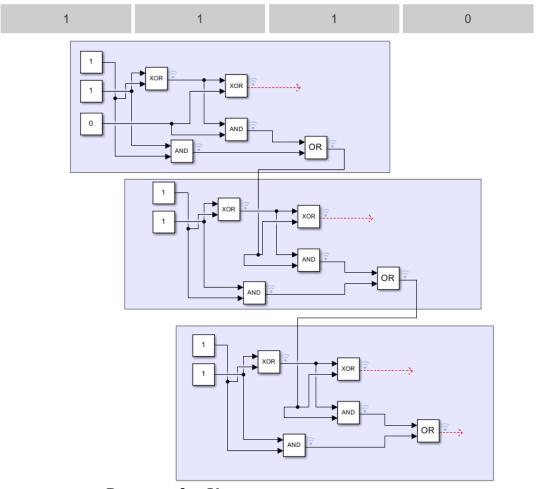

Одноразрядные сумматоры могут быть соединены между собой для построения двоичного каскадного сумматора.

Рисунок 3 – Каскад полных сумматоров

Такой каскад позволяет считать сумму трёхразрядных двоичных чисел. Таким образом, максимальное число, которое может быть получено: 111 + 111 = 1110. Количество каскадов можно увеличить, тогда появится возможность складывать большие числа.

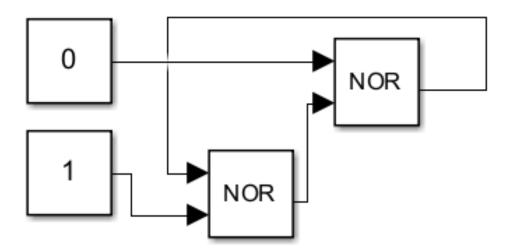

Тригтер — электронная схема, предназначенная для хранения значений одноразрядного двоичного кода. При воздействии на входы он переводится в одно из двух возможных состояний, при отсутствии входных сигналов сохраняет своё значение. Самый распространённый тип — RS-тригтер (от англ. reset и set). Его можно реализовать на двух логических элементах («ИЛИ-НЕ» и «И-НЕ»). На выходе, помимо текущего состояния тригтера, принято выводить и его инверсный сигнал (табл. 3).

Таблица 3 — Таблица истинности RS-триггера

| Режим<br>работы | S | R | Q | $\neg Q$ |

|-----------------|---|---|---|----------|

| Хранение        | 0 | 0 | 1 | 0        |

| Запись 1        | 1 | 0 | 1 | 0        |

| Запись 0        | 0 | 1 | 0 | 1        |

| Запрещение      | 1 | 1 | X | X        |

Логическая схема триггера имеет вид (рис. 4)

Рисунок 4 – Логическая схема RS-триггера в MATLAB & Simulink

Для хранения двоичного кода, и выполнения преобразований над ними используются регистры, они представляют собой упорядоченный набор триггеров.

#### 3. Выволы

Были рассмотрены основные устройства, составляющие арифметико логическое устройство вычислительных машин, построены схемы с использованием СКМ MATLAB & Simulink.

### Библиографический список

- 1. Болтовский Г. А. Построение логических схем с использованием системы компьютерной математики MATLAB&Simulink // Постулат, 2023. № 1.

- 2. Зюзьков В. М. Введение в математическую логику. Учебное пособие. М: Лань, 2018. 268 с.

- 3. Колмогоров А. Н., Драгалин А. Г. Математическая логика. Введение в математическую логику. М.: Ленанд. 2017. 240 с.

- 4. Харрис Д., Харрис С. Цифровая схемотехника и архитектура компьютера. Litres, 2022.

- 5. Мой компьютер на логических микросхемах URL: https://www.habr.com/ru/post/590821/ (дата обращения: 1.12.2022)

- 6. АЛУ на логических микросхемах URL: https://www.habr.com/ru/post/595367/ (дата обращения: 1.12.2022)

- 7. Проектирование собственного компьютера. URL: https://www.habr.com/ru/post/178071/ (дата обращения: 1.12.2022)